## **Product Specification**

**INDUSTRIAL**

CompactFlash Card

Version 01V1

Document No. 100-XXCFC-HATL

July 2016

APRO CO., LTD.

Phone: +88628226-1539 Fax: +88628226-1389 This document is for information use only and is **subject to change without prior notice**. APRO Co., Ltd. assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written consent of an officer of APRO Co., Ltd.

All parts of the APRO documentation are protected by copyright law and all rights are reserved.

APRO and the APRO logo are registered trademarks of APRO Co., Ltd.

Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

© 2016 APRO Corporation. All rights reserved.

#### **Revision History**

| Rev. | Description           | Update     |

|------|-----------------------|------------|

| 1.0  | Initial release       | 2013/10/1  |

| 1.1  | Add DWPD & TBW Value. | 2016/07/18 |

# **C**ONTENTS

| 1. | INTR  | ODUCTION                                               | 1 -    |

|----|-------|--------------------------------------------------------|--------|

|    | 1.1.  | SCOPE                                                  | 2 -    |

|    | 1.2.  | SYSTEM FEATURES                                        | 2 -    |

|    | 1.3.  | CFA 3.0 Specification                                  | 2 -    |

|    | 1.4.  | ATA/ATAPI-6 Standard                                   | 2 -    |

|    | 1.5.  | TECHNOLOGY INDEPENDENCE - STATIC WEAR LEVELING         | 2 -    |

|    | 1.6.  | CONFORMAL COATING                                      | 3 -    |

| 2. | PROL  | DUCT SPECIFICATIONS                                    | 4 -    |

|    | 2.1.  | SYSTEM ENVIRONMENTAL SPECIFICATIONS                    | 4 -    |

|    | 2.2.  | SYSTEM POWER REQUIREMENTS                              | 4 -    |

|    | 2.3.  | SYSTEM PERFORMANCE                                     | 4 -    |

|    | 2.4.  | SYSTEM RELIABILITY                                     | 5 -    |

|    | 2.5.  | PHYSICAL SPECIFICATIONS                                | 5 -    |

|    | 2.6.  | CAPACITY SPECIFICATIONS                                | 6 -    |

| 3. | INTE  | RFACE DESCRIPTION                                      | 7 -    |

|    | 3.1.  | CF INTERFACE (COMPACTFLASH TYPE I)                     | 7-     |

|    | 3.2.  | PIN ASSIGNMENTS                                        | 7 -    |

|    | 3.3.  | ELECTRICAL DESCRIPTION                                 | 10 -   |

| 4. | ELEC  | TRICAL SPECIFICATION                                   | - 16 - |

|    | 4.1.  | GENERAL DC CHARACTERISTICS                             | 16 -   |

|    | 4.1.1 | . Interface I/O at 5.0V                                | - 16 - |

|    | 4.1.2 | . Interface I/O at 3.3V                                | - 17 - |

|    | 4.2.  | AC CHARACTERISTICS                                     | 18 -   |

|    | 4.2.1 | . Attribute Memory Read Timing                         | - 18 - |

|    | 4.2.2 | . Configuration Register (Attribute Memory) Write Time | - 19 - |

|    | 4.2.3 | . Common Memory Read Timing                            | - 20 - |

|    | 4.2.4 | . Common Memory Write Timing                           | - 21 - |

|    | 4.2.5 | . I/O Read Timing                                      | - 22 - |

|    | 4.2.6 | . I/O Write Timing                                     | - 23 - |

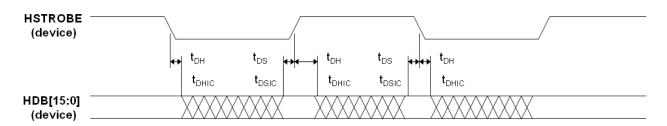

|    | 4.2.7 | . True IDE PIO Mode Read/Write Timing                  | - 24 - |

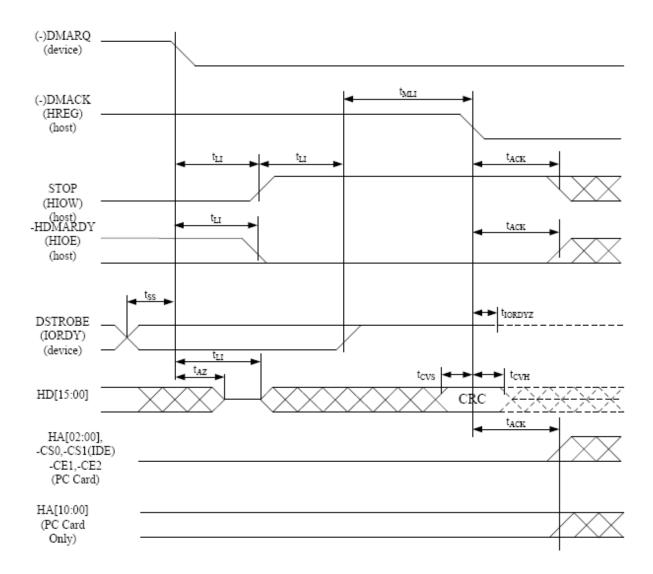

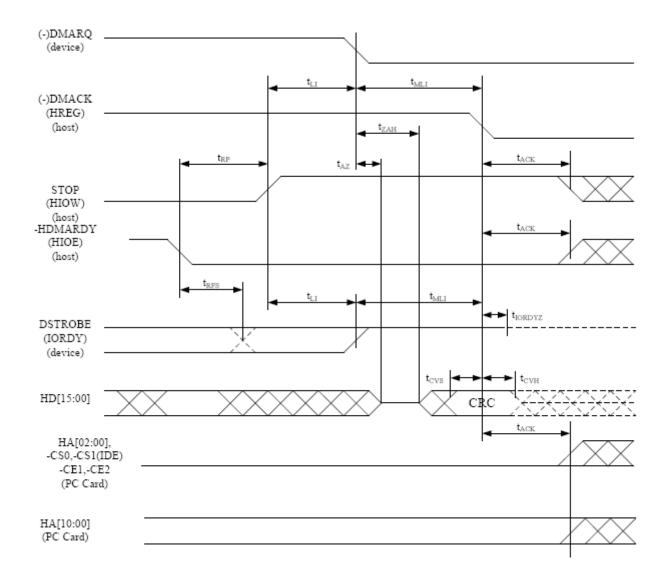

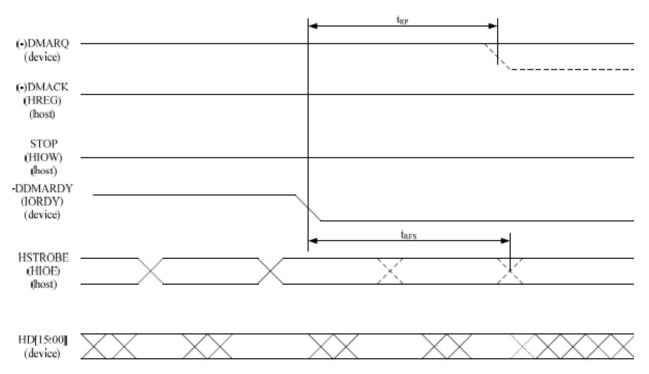

|    | 4.2.8 | . True IDE Multiword DMA Mode Read/Write Timing        | - 26 - |

|    | 4.2.9 | ,                                                      |        |

|    | 4.2.1 | 0. Ultra DMA Data Burst Timing Requirement             | - 29 - |

|    | 4.2.1            | 1. Ultra DMA Data Burst Timing Descriptions                  | 30 - |

|----|------------------|--------------------------------------------------------------|------|

|    | 4.2.1            | 2. Ultra DMA Sender and Recipient IC Timing Requirements     | 31 - |

|    | 4.2.1            | 3. Ultra DMA AC Signal Requirements                          | 32 - |

|    | 4.2.1            | 4. Ultra DMA Data-In Burst Initiation Timing                 | 32 - |

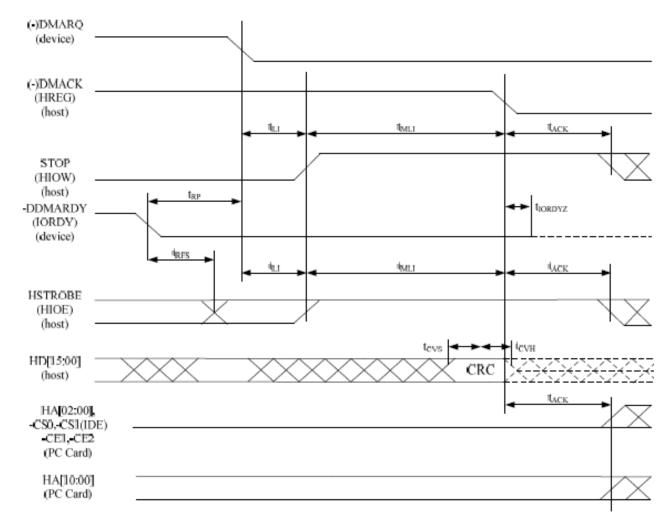

|    | 4.2.1            | 5. Sustained Ultra DMA Data-In Burst Timing                  | 33 - |

|    | 4.2.1            | 6. Ultra DMA Data-In Burst Host Pause Timing                 | 34 - |

|    | 4.2.1            | 7. Ultra DMA Data-In Burst Device Termination Timing         | 35 - |

|    | 4.2.1            | 8. Ultra DMA Data-In Burst Host Termination Timing           | 36 - |

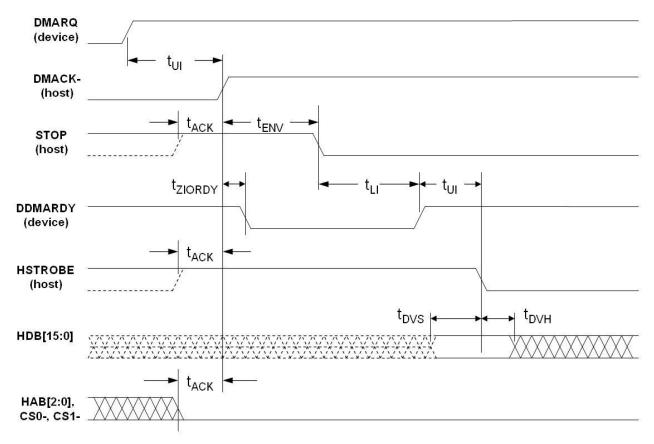

|    | 4.2.1            | 9. Ultra DMA Data-Out Burst Host Initiation Timing           | 37 - |

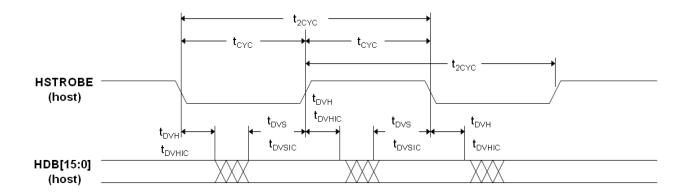

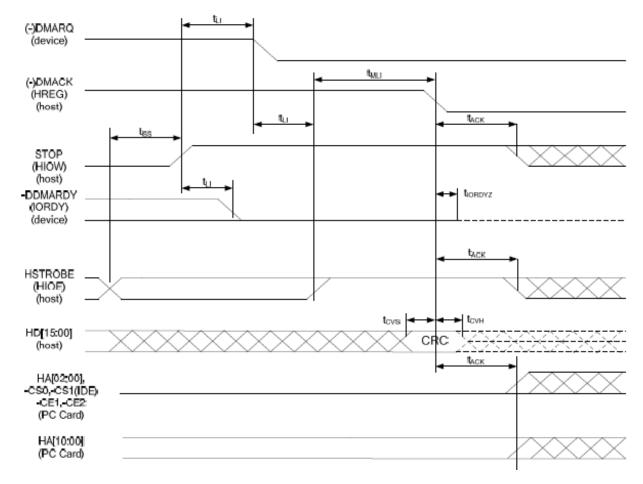

|    | 4.2.2            | 0. Sustained Ultra DMA Data-Out Burst Host Initiation Timing | 38 - |

|    | 4.2.2            | 1. Ultra DMA Data-Out Burst Device Pause Timing              | 39 - |

|    | 4.2.2            | 2. Ultra DMA Data-Out Burst Device Termination Timing        | 40 - |

|    | 4.2.2            | 3. Ultra DMA Data-Out Burst Host Termination Timing          | 41 - |

| 5. | INTE             | RFACE REGISTER DEFINITION                                    | 42 - |

|    |                  |                                                              |      |

|    | 5.1.             | DEVICE ADDRESS.                                              |      |

|    | 5.2.             | I/O REGISTER DESCRIPTIONS                                    | 42 - |

| 6. | SOFT             | WARE SPECIFICATION                                           | 44 - |

|    | 6.1.             | ATA COMMAND SET                                              | 44 - |

|    | 6.2.             | ATA COMMAND DESCRIPTION                                      | 45 - |

| 6. | .3. <i>S</i> N   | 1ART                                                         | 64 - |

|    |                  |                                                              |      |

|    | 6.3.1.           | SMART ENABLE OPERATION                                       |      |

|    | 6.3.2.           | SMART DISABLE OPERATION                                      |      |

|    | 6.3.3.           |                                                              |      |

|    | 6.3.4.           | SMART READ DATA                                              |      |

|    | 6.3.5.<br>6.3.6. | SPARE BLOCK COUNT ATTRIBUTE  ERASE COUNT ATTRIBUTE           |      |

|    | 6.3.7.           | TOTAL ECC ERRORS ATTRIBUTE                                   |      |

|    | 6.3.8.           | CORRECTABLE ECC ERRORS ATTRIBUTE                             |      |

|    | 6.3.9.           | TOTAL NUMBER OF READS ATTRIBUTE                              |      |

|    | 6.3.10.          | UDMA CRC Errors Attribute                                    |      |

|    | 6.3.11.          | SMART RETURN STATUS                                          |      |

|    | 6.3.11.          | SMART READ REMAP DATA                                        |      |

|    | 0.3.12.          |                                                              |      |

| Al | PPENDIX .        | A. ORDERING INFORMATION                                      | 70 - |

| Αl | PPENDIX          | B. LIMITED WARRANTY                                          | 72 - |

## **List of Tables**

| TABLE 1: ENVIRONMENTAL SPECIFICATION                            | 4-   |

|-----------------------------------------------------------------|------|

| TABLE 2: POWER REQUIREMENT                                      | 4 -  |

| TABLE 3: SYSTEM PERFORMANCES                                    | 4 -  |

| Table 4: System Reliability                                     | 5 -  |

| TABLE 5: PHYSICAL SPECIFICATIONS                                | 5 -  |

| Table 6: Device Parameter                                       | 6 -  |

| TABLE 7: PIN ASSIGNMENTS AND PIN TYPE                           | 7 -  |

| Table 8: Signal Description                                     | 10 - |

| Table 9: Electrical Condition                                   | 16 - |

| Table 10: Interface I/O at 5.0V                                 | 16 - |

| Table 11: Interface I/O at 3.3V                                 | 17 - |

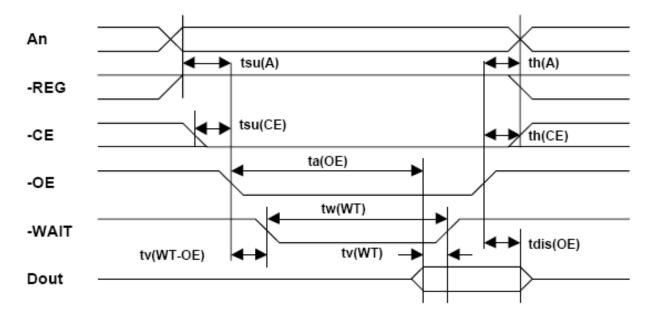

| Table 12: Attribute Memory Read Timing                          | 18 - |

| Table 13: Configuration Register (Attribute Memory) Write Time  | 19 - |

| Table 14: Common Memory Read Timing                             | 20 - |

| TABLE 15: COMMON MEMORY WRITE TIMING                            | 21 - |

| Table 16: I/O Read Timing                                       | 22 - |

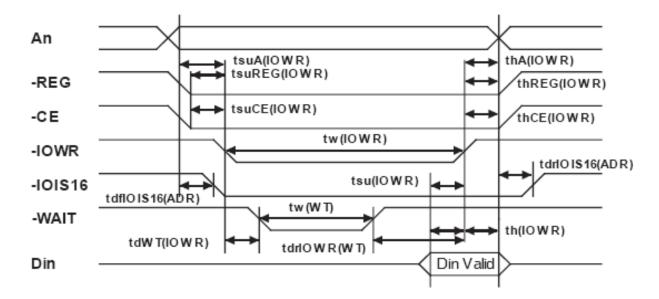

| TABLE 17: I/O WRITE TIMING                                      | 23 - |

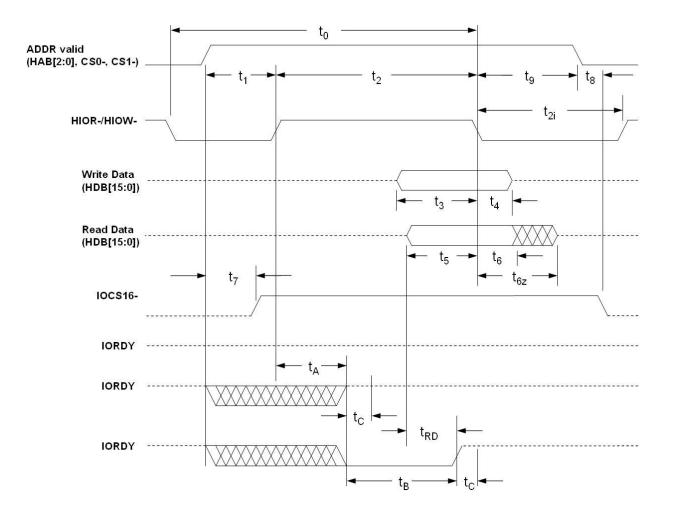

| TABLE 18: TRUE IDE PIO MODE READ/WRITE TIMING                   | 24 - |

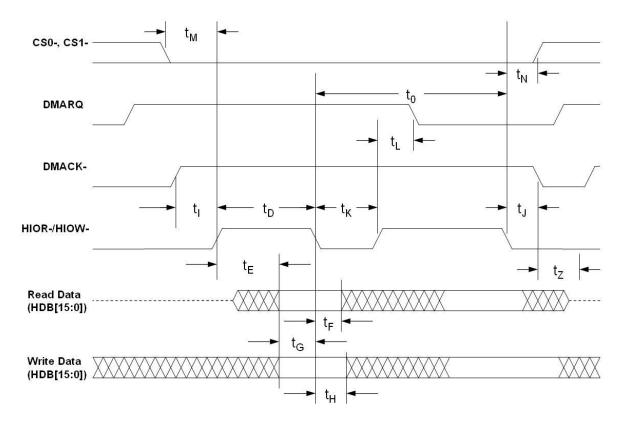

| TABLE 19: TRUE IDE MULTIWORD DMA MODE READ/WRITE TIMING         | 26 - |

| TABLE 20: ULTRA DMA SIGNAL IN TRUE IDE MODE                     | 28 - |

| TABLE 21: ULTRA DMA DATA BURST TIMING REQUIREMENT               | 29 - |

| TABLE 22: ULTRA DMA DATA BURST TIMING DESCRIPTIONS              | 30 - |

| TABLE 23: ULTRA DMA SENDER AND RECIPIENT IC TIMING REQUIREMENTS | 31 - |

| Table 24: Ultra DMA AC Signal Requirements                      | 32 - |

| TABLE 25: DEVICE ADDRESS COMMANDS                               | 42 - |

| Table 26: ATA Commands Supported                                | 44 - |

| Table 27: Diagnostic                                            | 46 - |

| TABLE 28: IDENTIFY DEVICE COMMANDS                              | 47 - |

| Table 29: Extended Error Codes                                  | 59 - |

| Table 30: Feature Supported                                     | 60 - |

## **List of Figures**

| FIGURE 1: COMPACTFLASH CARD HERMIT SERIES CONTROLLER BLOCK DIAGRAM       | 1 -  |

|--------------------------------------------------------------------------|------|

| FIGURE 2: COMPACTFLASH CARD DIMENSION                                    | 6 -  |

| FIGURE 3: 50-PIN COMPACTFLASH TYPE I CONNECTOR                           | 7 -  |

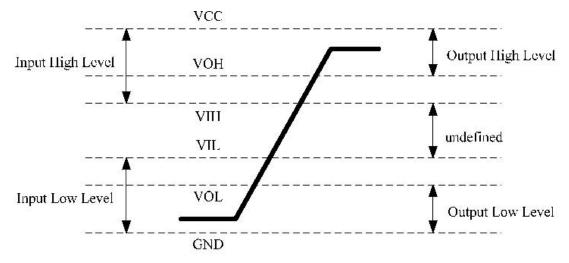

| FIGURE 4: INTERFACE I/O VOLTAGE DIAGRAM                                  | 17 - |

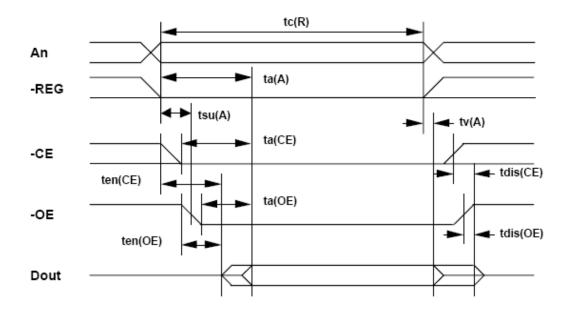

| FIGURE 5: ATTRIBUTE MEMORY READ TIMING DIAGRAM                           | 18 - |

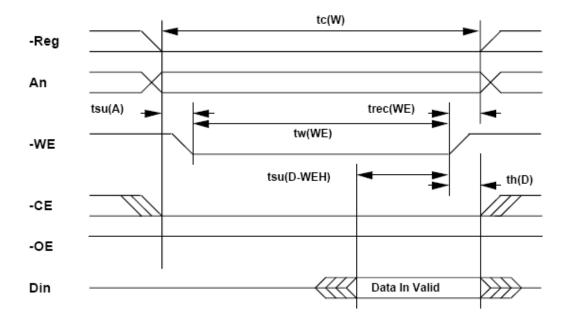

| FIGURE 6: CONFIGURATION REGISTER (ATTRIBUTE MEMORY) WRITE TIMING DIAGRAM | 19 - |

| FIGURE 7: COMMON MEMORY READ TIMING DIAGRAM                              | 20 - |

| FIGURE 8: COMMON MEMORY READ TIMING DIAGRAM                              | 21 - |

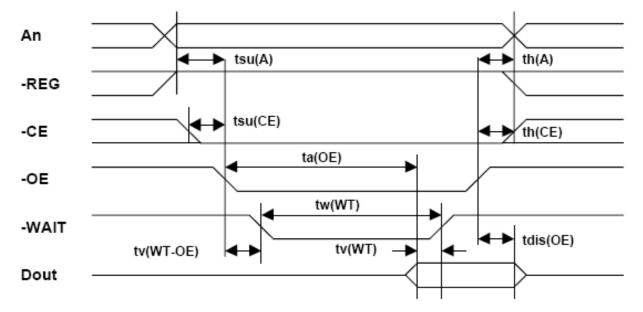

| FIGURE 9: I/O READ TIMING DIAGRAM                                        | 23 - |

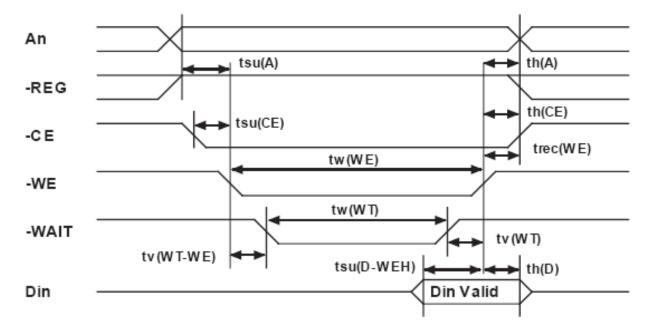

| FIGURE 10: I/O WRITE TIMING DIAGRAM                                      | 24 - |

| FIGURE 11: TRUE IDE PIO MODE READ/WRITE TIMING DIAGRAM                   | 25 - |

| FIGURE 12: TRUE IDE MULTIWORD DMA MODE READ/WRITE TIMING DIAGRAM         | 27 - |

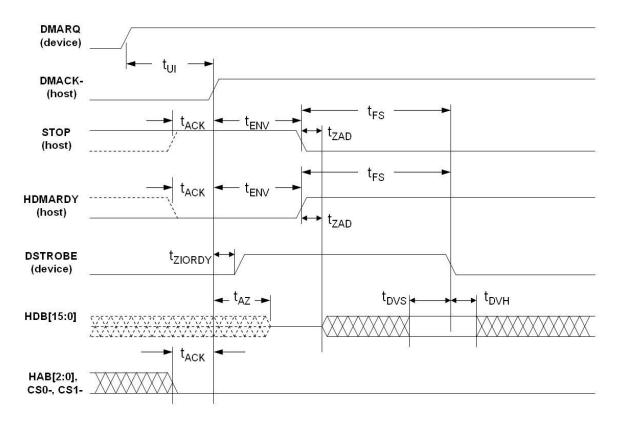

| FIGURE 13: ULTRA DMA DATA-IN BURST INITIATION TIMING DIAGRAM             | 32 - |

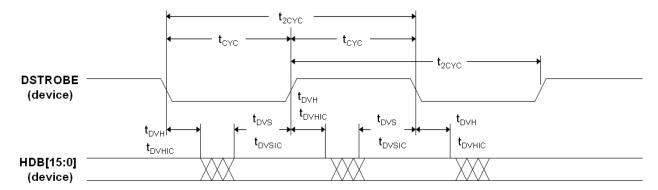

| FIGURE 14: SUSTAINED ULTRA DMA DATA-IN BURST INITIATION TIMING DIAGRAM   | 33 - |

| FIGURE 15: ULTRA DMA DATA-IN BURST HOST PAUSE TIMING DIAGRAM             | 34 - |

| FIGURE 16: ULTRA DMA DATA-IN BURST DEVICE TERMINATION TIMING DIAGRAM     | 35 - |

| FIGURE 17: ULTRA DMA DATA-IN BURST HOST TERMINATION TIMING DIAGRAM       | 36 - |

| FIGURE 18: ULTRA DMA DATA-OUT BURST INITIATION TIMING DIAGRAM            | 37 - |

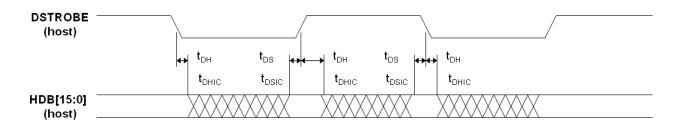

| FIGURE 19: SUSTAINED ULTRA DMA DATA-OUT BURST TIMING DIAGRAM             | 38 - |

| FIGURE 20: ULTRA DMA DATA-OUT BURST DEVICE PAUSE TIMING DIAGRAM          | 39 - |

| FIGURE 21: ULTRA DMA DATA-OUT BURST DEVICE TERMINATION TIMING DIAGRAM    | 40 - |

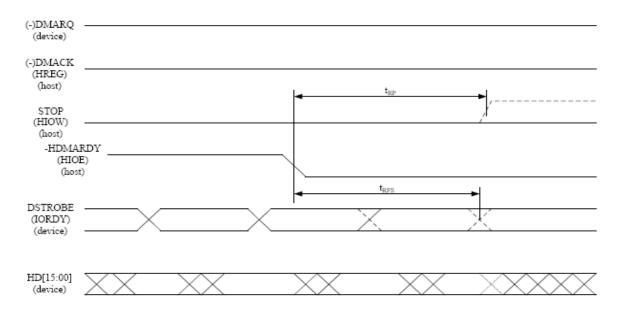

| FIGURE 22: ULTRA DMA DATA-OUT BURST HOST TERMINATION TIMING DIAGRAM      | 41 - |

#### 1. Introduction

APRO Industrial CompactFlash (CF) Card supports S.M.A.R.T. function – HERMIT Series designed to follow ATAPI-6 (ATA-100) standard. The main used Flash memories are SLC-NAND Type Flash memory chips from 16MB up to 8GB. The operating temperature grade is optional for commercial level 0°C ~ 70°C and wide temperature level -40°C ~ +85°C. The APRO Industrial CompactFlash (CF) Cards supports S.M.A.R.T. function - HERMIT Series are designed electrically complies with the conventional IDE hard Card and support True IDE Mode. The data transfer modes supports PIO mode 0, 1, 2, 3, 4 or MWDMA- 0, 1, 2 or UDMA- 0, 1, 2, 3, 4. The fastest reading speed is up to 37.8 MB/sec and writing speed is up to 27.0 MB/sec. In order to sustain various harsh and tough operating environments, APRO especially delivers the CompactFlash frame kit in rugged metal as well as provides the optional treatment of conformal coating upon customers' request.

The APRO Industrial CF card products provide a high level interface to the host computer. This interface allows a host computer to issue commands to the CompactFlash (CF) Card to read or write blocks of memory. Each sector is protected by a powerful 4 bits Error Correcting Code (ECC). APRO Industrial CompactFlash (CF) Card's HERMIT Series intelligent controller manages interface protocols, data storage and retrieval as well as ECC, defect handling and diagnostics, power management and clock control.

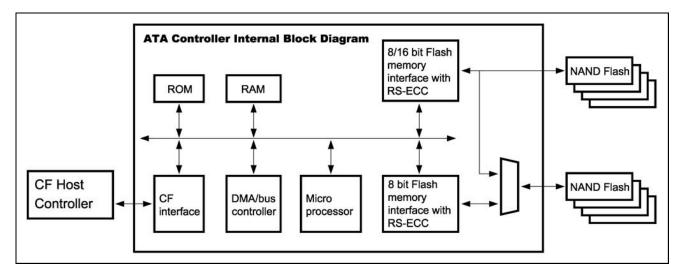

Figure 1 shows a block diagram of the used high tech Industrial CompactFlash (CF) Card controller.

Figure 1: CompactFlash Card HERMIT Series Controller Block Diagram

#### 1.1. Scope

This document describes the features and specifications and installation guide of APRO's Industrial CF Cards supports S.M.A.R.T. function – HERMIT Series. In the appendix, there provides order information, warranty policy, RMA/DOA procedure for the most convenient reference.

#### 1.2. System Features

- Optional Rugged metal CompactFlash casing to sustain the harshest environments

- SLC-NAND type flash technology

- Card capacity from 16MB to 8GB

- Supports S.M.A.R.T. function (Self-Monitoring, Analysis and Reporting Technology)

- ATA inter face and support PC Card Memory mode, PC Card I/O mode and True IDE mode

- Data transfer supports PIO-6 and UDMA-4 (Default setting)

- Sequential read: 37.8 MB/sec; Write: 27.0MB/sec. (1GB, max.)

- Automatic 4 bits error correction (ECC) and retry capabilities

- +5 V  $\pm 10\%$  or +3.3 V  $\pm 5\%$  operation

- MTBF 3,000,000 hours.

- Shock: 1,500G, compliance to MIL-STD-810F

- Vibration: 15G, compliance to MIL-STD-810F

- Work well in severe environments

- Very high performance, very low power consumption

- Low weight, Noiseless

- Conformal coating upon special request

#### 1.3. CFA 3.0 Specification

APRO Industrial CF card – HERMIT Series is fully compatible with the CFA 3.0 specification.

#### 1.4. ATA/ATAPI-6 Standard

APRO Industrial CF card – HERMIT Series is compliant to ATA/ATAPI-6 and below version.

#### 1.5. Technology Independence - Static Wear Leveling

In order to gain the best management for flash memory, APRO Industrial CF card – HERMIT Series supports Static Wear Leveling technology to manage the Flash system. The life of flash memory is limited; the management is to increase the life of the flash product.

A static wear-leveling algorithm evenly distributes data over an entire Flash cell array and searches for the least used physical blocks. The identified low cycled sectors are used to write the data to those locations. If blocks are empty, the write occurs normally. If blocks contain static data, it moves that data to a more heavily used location before it moves the newly written data. The static wear leveling maximizes effective endurance Flash array compared to no wear leveling or dynamic wear leveling.

#### 1.6. Conformal coating

Commonly used conformal coatings include silicone, acrylic, urethane and epoxy. APRO applies only silicone on APRO storages products upon requested especially by customers. The type of silicone coating features good thermal shock resistance due to flexibility. It is also easy to apply and repair.

Conformal coating offers protection of circuitry from moisture, fungus, dust and corrosion caused by extreme environments. It also prevents damage from those Flash storages handling during construction, installation and use, and reduces mechanical stress on components and protects from thermal shock. The greatest advantage of conformal coating is to allow greater component density due to increased dielectric strength between conductors.

APRO uses MIL-I-46058C silicon conformal coating.

## 2. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

## 2.1. System Environmental Specifications

Table 1: Environmental Specification

|             | APRO Industrial CF card - HERMIT Series | Commercial Grade                  | Industrial Grade |  |  |

|-------------|-----------------------------------------|-----------------------------------|------------------|--|--|

|             | Operating:                              | 0ºC ~ +70ºC                       | -40ºC ~ +85ºC    |  |  |

| Temperature | Non-operating:                          | -20ºC ~ +80ºC                     | -50ºC ~ +95ºC    |  |  |

| Humidity    | Operating & Non-operating:              | 10% ~ 95% non-condensing          |                  |  |  |

| Vibration   | Operating & Non-operating:              | 15G compliance to MIL-STD-810F    |                  |  |  |

| Shock       | Operating & Non-operating:              | 1,500G compliance to MIL-STD-810F |                  |  |  |

| Altitude    | Operating & Non-operating:              | 70,000 feet                       |                  |  |  |

## 2.2. System Power Requirements

**Table 2: Power Requirement**

| APRO Industrial CF card - HERMIT Series | Commercial Grade  | Industrial Grade |  |  |  |

|-----------------------------------------|-------------------|------------------|--|--|--|

| DC Input Voltage (VCC)                  | 5V±10% or 3.3V±5% |                  |  |  |  |

| Reading mode                            | 124 mA (Max)      |                  |  |  |  |

| Writing mode                            | 121 mA (Max)      |                  |  |  |  |

| Idle mode                               | 1.8 mA (Max)      |                  |  |  |  |

## 2.3. System Performance

**Table 3: System Performances**

|                                 | - PIO mode : 0, 1, 2, 3, 4, 5 ,6,(PIO – 6 defaulted) |           |                              |                                                     |         |           |           |            |             |         |      |       |

|---------------------------------|------------------------------------------------------|-----------|------------------------------|-----------------------------------------------------|---------|-----------|-----------|------------|-------------|---------|------|-------|

| Data Transfer Mode supporting   |                                                      |           | - DMA SW Mode: Not supported |                                                     |         |           |           |            |             |         |      |       |

|                                 |                                                      |           | - DMA M                      | W Mode:0                                            | 0,1, 2  |           |           |            |             |         |      |       |

|                                 | - UDMA I                                             | Mode: 0,1 | ,2,3, <b>4 (U</b> D          | MA-4 def                                            | aulted) |           |           |            |             |         |      |       |

| Data Transfer Rate To/From Host |                                                      |           |                              |                                                     | 16.6M   | ybtes/sec | burst und | er PIO Mod | de 4 as det | faulted |      |       |

| Data Iran                       | sier kate 10/Fron                                    | ii Host   |                              | 66.6Mbytes/sec burst under UDMA-4 Mode as defaulted |         |           |           |            |             |         |      |       |

| Ave                             | rage Access Time                                     |           | 0.2 ms(estimated)            |                                                     |         |           |           |            |             |         |      |       |

|                                 | Capac                                                | ity       | 16MB                         | 32MB                                                | 64MB    | 128MB     | 256MB     | 512MB      | 1GB         | 2GB     | 4GB  | 8GB   |

| Maximum                         | Sequential                                           | PIO- 6    | 4.0                          | 4.0                                                 | 4.0     | 4.0       | 4.0       | 4.0        | 4.7         | 4.7     | 4.7  | 4.6   |

| Performance                     | Read (MB/s)                                          | UDMA -4   | 17.15                        | 17.15                                               | 17.41   | 17.8      | 17.8      | 19.8       | 37.8        | 36.7    | 36.5 | 38.29 |

| Periormance                     | Sequential                                           | PIO- 6    | 4.2                          | 4.2                                                 | 4.2     | 4.2       | 4.2       | 4.0        | 4.6         | 4.6     | 4. 6 | 4.0   |

|                                 | Write(MB/s)                                          | UDMA -4   | 5.94                         | 5.94                                                | 6.02    | 11.2      | 11.2      | 13.7       | 27.0        | 26.4    | 26.6 | 16.59 |

| The number of Channel           |                                                      |           | Single                       | Single                                              | Single  | Single    | Single    | Single     | Dual        | Dual    | Dual | Dual  |

<sup>(1).</sup> All values quoted are typically at 25  ${\mathcal C}\,$  and nominal supply voltage.

<sup>(2).</sup> Testing of the Industrial CompactFlash (CF) Card maximum performance was performed under the following platform:

- Computer with AMD 3.0GHz processor

- Windows XP Professional operating system

- (3). Above performance data are for reference only for the performance would be different for various factors such like flash memory chips, system configuration and software for performance testing,...etc.

## 2.4. System Reliability

Table 4: System Reliability

| MTBF                     | 3,000,000 hours                            | ,000,000 hours                  |  |  |  |  |  |  |  |

|--------------------------|--------------------------------------------|---------------------------------|--|--|--|--|--|--|--|

| Wear-leveling Algorithms | tatic wear-leveling algorithms             |                                 |  |  |  |  |  |  |  |

| ECC Technology           | 4 bits per 512 bytes block                 | bits per 512 bytes block        |  |  |  |  |  |  |  |

| Erase counts             | NAND SLC Flash Cell Level : 60K P/E Cycles |                                 |  |  |  |  |  |  |  |

| Data Retention           | 10 years                                   |                                 |  |  |  |  |  |  |  |

| Capacity                 | TBW(TB)                                    | DWPD & Lifespan                 |  |  |  |  |  |  |  |

| 16MB                     | 0.8                                        |                                 |  |  |  |  |  |  |  |

| 32MB                     | 1.7                                        |                                 |  |  |  |  |  |  |  |

| 64MB                     | 3.3                                        |                                 |  |  |  |  |  |  |  |

| 128MB                    | 6.58                                       | Liference E Verre               |  |  |  |  |  |  |  |

| 256MB                    | 13.18                                      | Lifespan = 5 Years;  DWPD=29.62 |  |  |  |  |  |  |  |

| 512MB                    | 26.36                                      | DWPD ( Disk Written Per Day )   |  |  |  |  |  |  |  |

| 1GB                      | 52.73                                      | DWFD ( DISK WITHER FEI Day )    |  |  |  |  |  |  |  |

| 2GB                      | 105.46                                     |                                 |  |  |  |  |  |  |  |

| 4GB                      | 210.9                                      |                                 |  |  |  |  |  |  |  |

| 8GB                      | 421.8                                      |                                 |  |  |  |  |  |  |  |

## 2.5. Physical Specifications

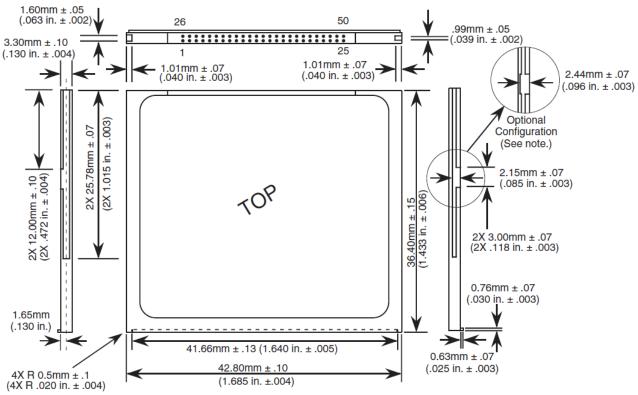

Refer to Table 5 and see Figure 2 for Industrial CF HERMIT Series physical specifications and dimensions.

**Table 5: Physical Specifications**

| Industrial CompactFlash Card ( Type I CompactFlash ) |                                                 |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|

| <b>Length:</b> 36.40±0.15mm(1.433±0.006 in)          |                                                 |  |  |  |  |  |

| Width:                                               | 42.80±0.10mm(1.685±0.004 in)                    |  |  |  |  |  |

| Thickness:                                           | 3.3mm±0.10mm(.130±0.004 in) (Excluding Lip)     |  |  |  |  |  |

| Weight:                                              | 12.0g(0.42oz) typical, 14.2 g (.0.5 oz) maximum |  |  |  |  |  |

Note: The optional notched configuration was shown in the CF Specification Rev. 1.0. In specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but it is not recommended.

Figure 2: CompactFlash Card Dimension

## 2.6. Capacity Specifications

The table 6 shows the specific capacity for the various models and the default number of heads, sectors/track and cylinders.

**Unformatted Capacity Default Cylinder Default Head Default Sector LBA Total Sectors 16MB** 248 4 32 31,744 **32MB** 500 8 16 64,000 64MB 500 8 32 112,000 128MB 480 16 32 245,760 256MB 984 16 32 503,808 **512MB** 1,001 16 63 1,009,008 1GB 2,002 16 63 2,018,016 2GB 4,003 16 63 4,035,024 4GB 8,070,048 8,006 16 63 8GB 16,000 16 63 16,128,000

Table 6: Device Parameter

## 3. Interface Description

## 3.1. CF interface (CompactFlash Type I)

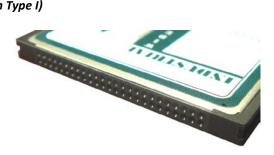

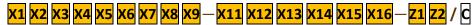

Figure 3: 50-pin CompactFlash Type I Connector

#### 3.2. Pin Assignments

Signals whose source is the host is designated as inputs while signals that the Industrial CompactFlash (CF) Card sources are outputs. The pin assignments are listed in below table 7.

The signal/pin assignments are listed in below Table 7. Low active signals have a "-" prefix. Pin types are Input, Output or Input/Output.

PC Card Memory Mode True IDE Mode<sup>4</sup> PC Card I/O Mode Signal In, Out Signal In, Out Signal In, Out Pin No. Pin Type Pin No. Pin Type Pin No. Pin Type Name Type Name Type Name Type GND Ground GND Ground GND Ground 1 1 1 11Z,OZ3 11Z,OZ3 2 D03 1/0 11Z,OZ3 D03 1/0 D03 1/0 11Z,OZ3 11Z,OZ3 1/0 11Z,OZ3 3 D04 1/0 D04 1/0 3 D04 1/0 11Z,OZ3 D05 4 D05 D05 1/0 11Z,OZ3 1/0 11Z,OZ3 D06 1/0 11Z,OZ3 D06 1/0 11Z,OZ3 D06 1/0 11Z,OZ3 1/0 11Z,OZ3 11Z,OZ3 D07 11Z,OZ3 6 D07 6 D07 1/0 6 1/0 7 -CE1 ī 13U 7 -CE1 ī 13U 7 -CSO 13Z  $A10^2$ 8 A10 Ī 11Z 8 A10 ī 11Z 8 11Z 9 -OE Ī 13U -OE Ī 13U -ATA SEL 13U A09<sup>2</sup> 10 A09 11Z 10 A09 11Z 10 11Z 11Z 11Z A08<sup>2</sup> 11Z 11 A08 11 A08 11 A07<sup>2</sup> 12 A07 Ī 11Z 12 A07 ī 11Z 12 11Z 13 VCC Power VCC Power VCC Power A06 11Z A06 11Z A06<sup>2</sup> 11Z 14 ı 11Z ī A05<sup>2</sup> 11Z 15 A05 15 A05 11Z 15 A04<sup>2</sup> A04 11Z A04 11Z 11Z 16 16 16 17 A03 Ī 11Z 17 A03 1 11Z 17 A03<sup>2</sup> 1 11Z 18 A02 11Z A02 11Z A02 11Z 18 18 19 A01 11Z 19 A01 11Z A01 11Z

Table 7: Pin Assignments and Pin Type

| PC Card Memory Mode |                   |          |         | PC Card I/O Mode |                   |          |         | True IDE Mode⁴ |                     |          |         |

|---------------------|-------------------|----------|---------|------------------|-------------------|----------|---------|----------------|---------------------|----------|---------|

|                     | Signal            |          | In, Out |                  | Signal            |          | In, Out |                | Signal              |          | In, Out |

| Pin No.             | Name              | Pin Type | Туре    | Pin No.          | Name              | Pin Type | Туре    | Pin No.        | Name                | Pin Type | Туре    |

| 20                  | A00               | ı        | 11Z     | 20               | A00               | I        | 11Z     | 20             | A00                 | I        | 11Z     |

| 21                  | D00               | 1/0      | 11Z,OZ3 | 21               | D00               | 1/0      | 11Z,OZ3 | 21             | D00                 | 1/0      | 11Z,OZ3 |

| 22                  | D01               | 1/0      | 11Z,OZ3 | 22               | D01               | 1/0      | 11Z,OZ3 | 22             | D01                 | I/O      | 11Z,OZ3 |

| 23                  | D02               | 1/0      | 11Z,OZ3 | 23               | D02               | 1/0      | 11Z,OZ3 | 23             | D02                 | I/O      | 11Z,OZ3 |

| 24                  | WP                | 0        | ОТ3     | 24               | -IOIS16           | 0        | ОТ3     | 24             | -IOCS16             | О        | ON3     |

| 25                  | -CD2              | 0        | Ground  | 25               | -CD2              | 0        | Ground  | 25             | -CD2                | 0        | Ground  |

| 26                  | -CD1              | 0        | Ground  | 26               | -CD1              | 0        | Ground  | 26             | -CD1                | 0        | Ground  |

| 27                  | D11 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 27               | D11 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 27             | D11 <sup>1</sup>    | I/O      | 11Z,OZ3 |

| 28                  | D12 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 28               | D12 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 28             | D12 <sup>1</sup>    | I/O      | 11Z,OZ3 |

| 29                  | D13 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 29               | D13 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 29             | D13 <sup>1</sup>    | I/O      | 11Z,OZ3 |

| 30                  | D14 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 30               | D14 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 30             | D14 <sup>1</sup>    | I/O      | 11Z,OZ3 |

| 31                  | D15 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 31               | D15 <sup>1</sup>  | 1/0      | 11Z,OZ3 | 31             | D15 <sup>1</sup>    | I/O      | 11Z,OZ3 |

| 32                  | -CE2 <sup>1</sup> | ı        | 13U     | 32               | -CE2 <sup>1</sup> | I        | 13U     | 32             | -CS1 <sup>1</sup>   | I        | 13Z     |

| 33                  | -VS1              | 0        | Ground  | 33               | -VS1              | 0        | Ground  | 33             | -VS1                | 0        | Ground  |

|                     |                   |          |         |                  |                   |          |         |                | -IORD <sup>7</sup>  |          |         |

|                     |                   |          |         |                  |                   |          |         |                | HSTROBE             |          |         |

| 34                  | -IORD             | 1        | 13U     | 34               | -IORD             | 1        | 13U     | 34             | 8                   | ı        | 13Z     |

|                     |                   |          |         |                  |                   |          |         |                | -HDMAR              |          |         |

|                     |                   |          |         |                  |                   |          |         |                | DY <sup>9</sup>     |          |         |

|                     |                   |          |         |                  |                   |          |         |                | -IOWR <sup>7</sup>  |          | 107     |

| 35                  | -IOWR             | I        | 13U     | 35               | -IOWR             | I        | 13U     | 35             | STOP <sup>8.9</sup> | ı        | 13Z     |

| 36                  | -WE               | ı        | 13U     | 36               | -WE               | ı        | 13U     | 36             | -WE <sup>3</sup>    | I        | 13U     |

| 37                  | READY             | 0        | OT1     | 37               | -IREQ             | 0        | OT1     | 37             | INTRQ               | 0        | OZ1     |

| 38                  | vcc               |          | Power   | 38               | VCC               |          | Power   | 38             | VCC                 |          | Power   |

| 39                  | -CSEL⁵            | I        | 12Z     | 39               | -CSEL⁵            | ı        | 12Z     | 39             | -CSEL               | ı        | 12U     |

| 40                  | -VS2              | 0        | OPEN    | 40               | -VS2              | 0        | OPEN    | 40             | -VS2                | 0        | OPEN    |

| 41                  | RESET             | I        | 12Z     | 41               | RESET             | I        | 12Z     | 41             | -RESET              | I        | 12Z     |

|                     |                   |          |         |                  |                   |          |         |                | IORDY <sup>7</sup>  |          |         |

|                     |                   |          |         |                  |                   |          |         |                | -DDMAR              |          |         |

| 42                  | -WAIT             | 0        | OT1     | 42               | -WAIT             | 0        | OT1     | 42             | DY <sup>8</sup>     | О        | ON1     |

|                     |                   |          |         |                  |                   |          |         | DSTROBE        |                     |          |         |

|                     |                   |          |         |                  |                   |          |         |                | 9                   |          |         |

| 43                  | -INPACK           | 0        | OT1     | 43               | -INPACK           | 0        | OT1     | 43             | DMARQ               | 0        | OZ1     |

| 44                  | -REG              | ı        | 13U     | 44               | -REG              | I        | 13U     | 44             | -DMACK <sup>6</sup> | ı        | 13U     |

| 45                  | BVD2              | 0        | OT1     | 45               | -SPKR             | 0        | OT1     | 45             | -DASP               | I/O      | 11U,ON1 |

|         | PC Card Memory Mode |          |                 |         | PC Card I/O Mode |          |                 |         | True IDE Mode <sup>4</sup> |          |         |  |

|---------|---------------------|----------|-----------------|---------|------------------|----------|-----------------|---------|----------------------------|----------|---------|--|

| Pin No. | Signal<br>Name      | Pin Type | In, Out<br>Type | Pin No. | Signal<br>Name   | Pin Type | In, Out<br>Type | Pin No. | Signal<br>Name             | Pin Type | In, Out |  |

| 46      | BVD1                | 0        | OT1             | 46      | -STSCHG          | 0        | OT1             | 46      | -PDIAG                     | 1/0      | 11U.ON1 |  |

| 47      | D08 <sup>1</sup>    | 1/0      | 11Z,OZ3         | 47      | D08 <sup>1</sup> | 1/0      | 112,023         | 47      | D08 <sup>1</sup>           | 1/0      | 11Z,OZ3 |  |

| 48      | D09 <sup>1</sup>    | 1/0      | 11Z,OZ3         | 48      | D09 <sup>1</sup> | 1/0      | 11Z,OZ3         | 48      | D09 <sup>1</sup>           | 1/0      | 11Z,OZ3 |  |

| 49      | D10 <sup>1</sup>    | I/O      | 11Z,OZ3         | 49      | D10 <sup>1</sup> | 1/0      | 11Z,OZ3         | 49      | D10 <sup>1</sup>           | 1/0      | 11Z,OZ3 |  |

| 50      | GND                 |          | Ground          | 50      | GND              |          | Ground          | 50      | GND                        |          | Ground  |  |

- 1) These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 3-state signals not to consume current.

- 2) The signal should be grounded by the host.

- 3) The signal should be tied to VCC by the host.

- 4) The mode is optional for CF+ Cards, but required for CompactFlash Cards.

- 5) The -CSEL signal is ignored by the card in PC Card modes. However, because it is not pulled up on the card in these modes, it should not be left floating by the host in PC Card modes. In these modes, the pin should be connected by the host to PC Card A25 or grounded by the host.

- 6) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA operations are not active, the card shall ignore this signal, including a floating condition

- 7) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

- 8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Write is active.

- 9) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

#### 3.3. Electrical Description

The APRO Industrial CompactFlash Card -HERMIT Series is optimized for operation with hosts, which support the PCMCIA/ I/O interface standard conforming to the PC Card ATA specification. However, the CompactFlash Card may also be configured to operate in systems that support only the memory interface standard. The configuration of the CompactFlash Card will be controlled using the standard PCMCIA configuration registers starting at address 200h in the Attribute Memory space of the CompactFlash Card.

Table 8: describes the I/O signals. Signals whose source is the host are designated as inputs while signals that the CompactFlash Card sources are outputs. The CompactFlash Card logic levels conform to those specified in the *PCMCIA Release 2.1 Specification*. See Section 3.3 for definitions of Input and Output type.

**Table 8: Signal Description**

| Signal Name           | Dir | Pin            | Description                                                                 |  |

|-----------------------|-----|----------------|-----------------------------------------------------------------------------|--|

| A10 – A0              |     |                | These address lines along with the –REG signal are used to select the       |  |

| (PC Card Memory Mode) |     | 8,10,11,12,14, | following: The I/O port address registers within the CompactFlash Card or   |  |

|                       | 1   | 15,16,17,18,19 | CF+ Card, the memory mapped port address registers within the               |  |

|                       |     | ,20            | CompactFlash Card or CF+ Card, a byte in the card's information structure   |  |

|                       |     |                | and its configuration control and status registers.                         |  |

| A10 – A0              |     |                | This signal is the same as the PC Card Memory Mode signal.                  |  |

| (PC Card I/O Mode)    |     |                | This signal is the same as the PC Card Memory Mode Signal.                  |  |

| A2 – A0               |     |                | In True IDE Mode, only A[2:0] are used to select the one of eight registers |  |

| (True IDE Mode)       | 1   | 18,19,20       | in the Task File, the remaining address lines should be grounded by the     |  |

|                       |     |                | host.                                                                       |  |

| BVD1                  | I/O | 46             | This signal is asserted high, as BVD1 is not supported                      |  |

| (PC Card Memory Mode) | 170 | 40             | This signal is asserted high, as BVD1 is not supported.                     |  |

| -STSCHG               |     |                | This signal is asserted low to alert the host to changes in the READY and   |  |

| (PC Card I/O Mode)    |     |                | Write Protect states, while the I/O interface is configured. It use is      |  |

| Status Changed        |     |                | controlled by the Card Config and Status Register.                          |  |

| -PDIAG                |     |                | In the True IDE Mode, this input / output is the Pass Diagnostic signal in  |  |

| (True IDE Mode)       |     |                | the Master / Slave handshake protocol.                                      |  |

| BVD2                  | I/O | 45             | This signal is asserted high, as DVD3 is not supported                      |  |

| (PC Card Memory Mode) | 1/0 | 45             | This signal is asserted high, as BVD2 is not supported.                     |  |

| -SPKR                 |     |                | This line is the Binary Audio output from t he card. If the Card does not   |  |

| (PC Card I/O Mode)    |     |                | support the Binary Audio function, this line should be held negated.        |  |

| -DASP                 |     |                | In the True IDE Mode, this input/output is the Disk Active/Slave Present    |  |

| (True IDE Mode)       |     |                | signal in the Master/Slave handshake protocol.                              |  |

| -CD1, -CD2            | _   |                | These Card Detect pins are connected to ground on the CompactFlash          |  |

| (PC Card Memory Mode) | О   | 26,25          | Card or CF+ Card. They are used by the host to determine that the           |  |

|                       |     |                | CompactFlash Card or CF+ Card is fully inserte4d into its socket.           |  |

| Signal Name                       | Dir | Pin             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------------------------------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -CD1, -CD2                        |     |                 | This signal is the same for all modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| (PC Card I/O Mode)                |     |                 | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| -CD1, -CD2                        |     |                 | This signal is the agent for all sender                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| (True IDE Mode)                   |     |                 | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| -CE1, -CE2                        |     |                 | These input signals are used both to select the card and to indicate to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| (PC Card Memory Mode) Card Enable |     |                 | card whether a byte or a word operation is being performed. –CE2 always                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                   | 1   | 7,32            | accesses the odd byte of the word. –CE1 accesses the even byte or the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                   |     |                 | Odd byte of the word depending on A0 and –CE2. A multiplexing scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                   |     |                 | based on A0, -CE1, -CE2 allows 8 bit hosts to access all data on D0-D7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| -CE1, -CE2                        |     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| (PC Card I/O Mode)                |     |                 | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Card Enable                       |     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| -CS0, -CS1                        |     |                 | In the True IDE Mode, -CSO is the chip select for the task file registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| (True IDE Mode)                   |     |                 | while –CS1 is used to select the Alternate Status Register and the Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |