Nov. 2008 Rev. 1.0

# Product Specification Industrial micro IDE Flash Disk (MIF) - Hermit Series -

Doc-No: 100-XMIFHA-01V0

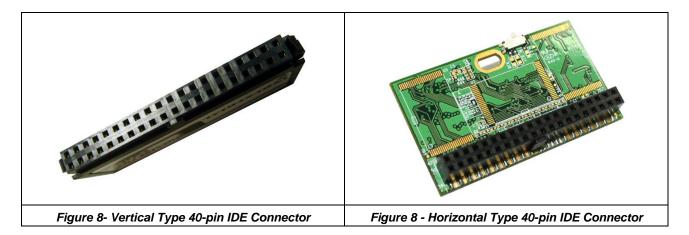

40/44-pin Horizontal

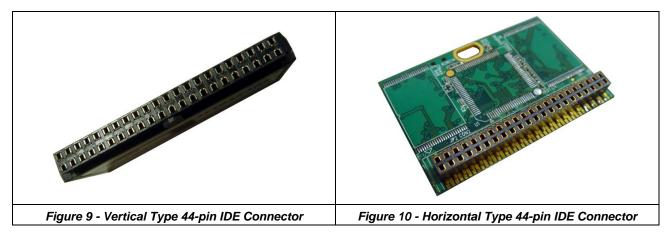

40/44-pin Vertical

This document is for information use only and is **subject to change without prior notice**. APRO Co., Ltd. assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written consent of an officer of APRO Co., Ltd..

All parts of the APRO documentation are protected by copyright law and all rights are reserved.

APRO and the APRO logo are registered trademarks of APRO Co., Ltd..

Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

© 2008 APRO Corporation. All rights reserved.

Revision History Rev. 1.0 —initial release

2008/12/23

# **C**ONTENTS

| 1.     | INTRODUCTION                                   |  |  |  |  |

|--------|------------------------------------------------|--|--|--|--|

| 1.1.   | <i>SCOPE</i>                                   |  |  |  |  |

| 1.2.   | SYSTEM FEATURES                                |  |  |  |  |

| 1.3.   | ATA/ATAPI-6 STANDARD                           |  |  |  |  |

| 1.4.   | TECHNOLOGY INDEPENDENCE - STATIC WEAR LEVELING |  |  |  |  |

| 2.     | PRODUCT SPECIFICATIONS                         |  |  |  |  |

| 2.1.   | SYSTEM ENVIRONMENTAL SPECIFICATIONS            |  |  |  |  |

| 2.2.   | SYSTEM POWER REQUIREMENTS                      |  |  |  |  |

| 2.3.   | SYSTEM PERFORMANCE                             |  |  |  |  |

| 2.4.   | System Reliability                             |  |  |  |  |

| 2.5.   | PHYSICAL SPECIFICATIONS                        |  |  |  |  |

| 2.6.   | CAPACITY SPECIFICATIONS                        |  |  |  |  |

| 3.     | INTERFACE DESCRIPTION                          |  |  |  |  |

| 3.1.   | PHYSICAL DESCRIPTION                           |  |  |  |  |

| 3.2.   | PINASSIGNMENTS                                 |  |  |  |  |

| 3.3.   | ELECTRICAL DESCRIPTION                         |  |  |  |  |

| 3.4.   | ELECTRICAL SPECIFICATION11                     |  |  |  |  |

| 3.4.1. | ABSOLUTE MAXIMUM RATING11                      |  |  |  |  |

| 3.4.2. | <b>Recommended Operating Condition</b> 11      |  |  |  |  |

| 3.4.3. | DC CHARACTERISTICS                             |  |  |  |  |

| 3.4.4. | TIMING SPECIFICATIONS                          |  |  |  |  |

| PIO N  | PIO MODE                                       |  |  |  |  |

| MULI   | MULTIWORD DMA                   |  |  |  |  |

|--------|---------------------------------|--|--|--|--|

| ULTR   | A DMA MODE                      |  |  |  |  |

| 4.     | COMMAND DESCRIPTIONS            |  |  |  |  |

| 4.1.   | <i>COMMAND SET</i>              |  |  |  |  |

| 5.     | INSTALLATION PROCEDURE          |  |  |  |  |

| 5.1.   | Before unpacking                |  |  |  |  |

| 5.2.   | ESD PRECAUTIONS                 |  |  |  |  |

| 5.3.   | CONFIGURATION OF MIF            |  |  |  |  |

| 5.4.   | MIF INSERTION AND REMOVING      |  |  |  |  |

| 5.4.1. | MIF INSERTION                   |  |  |  |  |

| 5.4.2. | MIF REMOVING                    |  |  |  |  |

| 5.5.   | IDE DEVICE SETUP/AUTO-DETECTION |  |  |  |  |

| 5.6.   | PARTITION & FORMAT              |  |  |  |  |

| Orde   | RING INFORMATION                |  |  |  |  |

| APPE   | NDIX A. LIMITED WARRANTY        |  |  |  |  |

# 1. Introduction

APRO Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series products are designed to follow ATA/ATAPI-6 standard. The main used Flash memories are Samsung SLC NAND Type Flash memory chips. The available Card capacities are 128MB, 256MB, 512MB, 1GB, 2GB, 4GB and 8GB. The operating temperature grade is optional for standard grade 0°C ~ 70°C and industrial grade -40°C ~ +85°C. The APRO Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series are designed electrically compliant with the conventional IDE hard disk and support True IDE Mode. The data transfer modes supports PIO mode 0~6, Multi Word DMA 0~4, or UDMA 0~5; Default setting are PIO mode-4 or UDMA-4. Hermit Series MIF features an extremely light weight, reliable, low-profile form factor.

The APRO Industrial 40/44-pin MIF Hermit Series provides a high level interface to the host computer. This interface allows a host computer to issue commands to the Flash Disk to read or write blocks of memory. The host addresses the card in 512 byte sectors. Each sector is protected by a powerful 4 bits Error Correcting Code (ECC). APRO Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series, it uses intelligent controller which manages interface protocols, data storage and retrieval as well as ECC, defect handling and diagnostics, power management and clock control.

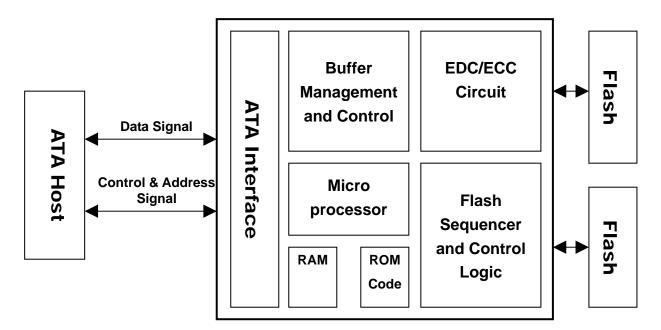

Figure 1 shows a block diagram of the used high tech Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series controller.

#### Figure 1: micro IDE Flash Disk Controller Block Diagram

### 1.1. Scope

This document describes the features and specifications and installation guide of APRO's Industrial 40/44-pin MIF Hermit Series. In the appendix, there provides order information, warranty policy, RMA/DOA procedure for the most convenient reference.

#### 1.2. System Features

- Non-volatile memory and no moving parts

- SLC NAND type flash technology

- Disk capacity from 128MB to 8GB

- ATA interface and True IDE mode

- Master/Slave Switch

- Data transfer supports PIO-4 and UDMA-4 (Default setting)

- Performance up to 40.0MB/sec

- Automatic 4 bits error correction and retry capabilities

- Supports power down commands and Auto stand-by / sleep modes.

- +5 V ±10% or +3.3 V ±5% operation

- MTBF > 3,000,000 hours.

- Shock : 50g (Duration : 10ms, 3 axes), compliance to IEC 68-2-27

- Vibration : 5g (7 Hz to 2000 Hz, 3 axes), compliance to IEC 68-2-6

- Rugged environment is working well

- Very high performance, very low power consumption

- Low weight, Noiseless

# 1.3. ATA/ATAPI-6 Standard

APRO Industrial 40/44-pin MIF disks are fully compatible with the ATA/ATAPI-6 standard.

#### 1.4. Technology Independence - Static Wear Leveling

In order to gain the best management for flash memory, APRO Industrial CF Cards - Hermit series supports Static

*Wear Leveling technology* to manage the Flash system. The life of flash memory is limited; the management is to increase the life of the flash product.

A static wear-leveling algorithm evenly distributes data over an entire Flash cell array and searches for the least used physical blocks. The identified low cycled sectors are used to write the data to those locations. If blocks are empty, the write occurs normally. If blocks contain static data, it moves that data to a more heavily used location before it moves the newly written data. The static wear leveling maximizes effective endurance Flash array compared to no wear leveling or dynamic wear leveling.

# 2. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

### 2.1. System Environmental Specifications

| rabio n'Ennional opernoution  |                            |                               |                        |  |

|-------------------------------|----------------------------|-------------------------------|------------------------|--|

|                               |                            | Standard Grade                | Industrial Grade       |  |

| APRO Industrial Hermit Series | MIF                        | SxMIFxxxx-HACSC Series        | WxMIFxxx-HAISI- Series |  |

| Temperature Operating:        |                            | 0°C ~ +70°C                   | -40°C ~ +85°C          |  |

|                               | Non-operating:             | -55°C ~ +95°C                 | -55°C ~ +95°C          |  |

| Humidity                      | Operating & Non-operating: | 10% ~ 95% non-condensing      |                        |  |

| Vibration                     | Operating & Non-operating: | 5g (7 Hz to 2000 Hz, 3 axes), |                        |  |

|                               |                            | compliance to IEC 68-2-6      |                        |  |

| Shock                         | Operating & Non-operating: | 50g (Duration:10ms, 3 axes),  |                        |  |

|                               |                            | compliance to IEC 68-2-27     |                        |  |

#### 2.2. System Power Requirements

#### Table 2: Power Requirement

|                                               |                 | Standard Grade                                          | Industrial Grade             |

|-----------------------------------------------|-----------------|---------------------------------------------------------|------------------------------|

| APRO Industrial Hermit Series MIF             |                 | SxMIFxxxx-HACSC Series                                  | WxMIFxxx-HAISI- Series       |

| DC Input Voltage (VCC) 100mV max. ripple(p-p) |                 | +5 V ±10%                                               |                              |

|                                               | Reading Mode :  | Single Channel: 69mA (max.)                             | / Duel Channel: 128mA (max.) |

| +5V Current                                   | Writing Mode :  | Single Channel: 48mA (max.) / Duel Channel: 118mA (max. |                              |

| (Maximum average value)                       | Sleeping Mode : | Single Channel: 1.2mA (max.)                            | / Duel Channel: 1.8mA (max.) |

#### 2.3. System Performance

#### Table 3: System Performances

| Data Transfer Mode supporting   |                  | - PIO mode : 0,1,2,3,4,5,6 (Default PIO-4)<br>- UDMA Mode: 0,1,2,3,4,5 (Default UDMA-4) |

|---------------------------------|------------------|-----------------------------------------------------------------------------------------|

| Data Transfer Rate To/Form Host |                  | 16.6Mybtes/sec burst under PIO Mode 4<br>66.6Mbytes/sec burst under UDMA-4 Mode         |

| Average Access Time             |                  | 0.2 ms(estimated)                                                                       |

| Maria Data                      | Sequential Read  | 40 Mbytes/sec Max.                                                                      |

| Maximum Performance             | Sequential Write | 17 Mbytes/sec Max.                                                                      |

Note:

(1). All values quoted are typically at 25oC and nominal supply voltage.

(2). Testing of the Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series maximum performance was performed under the following platform:

- Computer with AMD 3.0GHz processor

- Windows XP Professional operating system

- IDE transfer mode: Ultra DMA mode 4

- IDE Flash Disk capacity: 4GB

# 2.4. System Reliability

| МТВБ                     | >3,000,000 hours                                                                                                |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| Data Reliability         | <1 non-recoverable error in 10 <sup>14</sup> bits read<br><1 erroneous correction in 10 <sup>20</sup> bits read |  |  |  |

| Wear-leveling Algorithms | Supportive                                                                                                      |  |  |  |

| ECC Technology           | 4 bits Error Connection Code                                                                                    |  |  |  |

| Endurance                | Greater than 2,000,000 cycles Logically contributed by Wear-leveling and advanced bad sector management         |  |  |  |

| Data Retention           | 10 years                                                                                                        |  |  |  |

#### Table 4: System Reliability

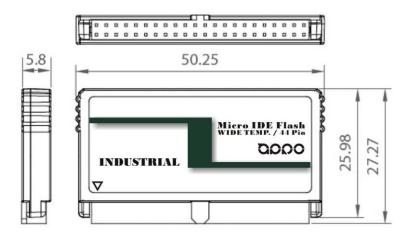

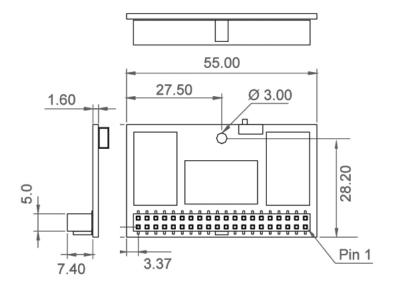

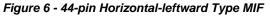

#### 2.5. Physical Specifications

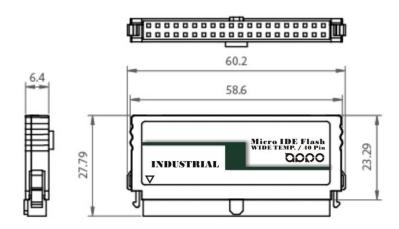

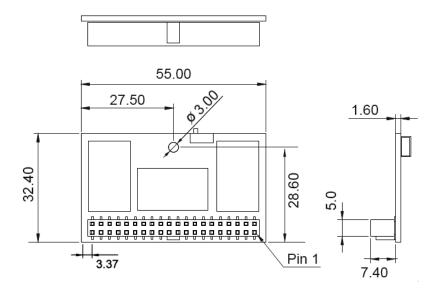

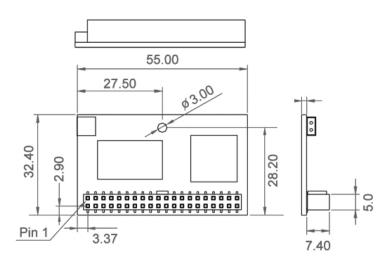

Refer to Table 5 and see Figure 3 for Industrial 40/44-pin MIF physical specifications and dimensions.

| rable 5. Filysical Specifications           |          |          |  |  |  |  |  |

|---------------------------------------------|----------|----------|--|--|--|--|--|

| 40-pin MIF                                  |          |          |  |  |  |  |  |

| Orientation : Vertical Type Horizontal Type |          |          |  |  |  |  |  |

| Length:                                     | 60.20 mm | 55.00 mm |  |  |  |  |  |

| Width:                                      | 27.79 mm | 32.40 mm |  |  |  |  |  |

| Thickness:                                  | 6.40 mm  | 7.40 mm  |  |  |  |  |  |

| G. W. :                                     | 20 gw    | 15 gw    |  |  |  |  |  |

| 44-pin MIF                                  |          |          |  |  |  |  |  |

| Orientation : Vertical Type Horizontal Type |          |          |  |  |  |  |  |

| Length: 50.25 mm 48.00 mm                   |          |          |  |  |  |  |  |

| Width:                                      | 32.60 mm |          |  |  |  |  |  |

| Thickness:      5.80 mm      4.50 mm        |          |          |  |  |  |  |  |

| <b>G. W.</b> : 15 gw 10 gw                  |          |          |  |  |  |  |  |

#### Table 5: Physical Specifications

Figure 2 - 40-pin Vertical Type MIF

Figure 3 – 40-pin Horizontal-leftward Type MIF

Figure 4 - 40-pin Horizontal-rightward Type MIF

Figure 5 - 44-pin Vertical Type MIF

Figure 7 - 44-pin Horizontal-rightward Type MIF

# 2.6. Capacity Specifications

APRO Industrial 40/44-pin micro IDE Flash (MIF) Disks are built-in mainly Samsung NAND Type SLC Flash memory chips. The Table 6 shows the equipollent part number of applied Samsung Flash memory chips for each card.

| Card Capacity |                   | g SLC Flash Memory Part Number * Q'TY    |

|---------------|-------------------|------------------------------------------|

|               | Standard Grade:   | K9F1G08U0A-PCB0(1Gb) or equipollent * 1  |

| 128MB         | Industrial Grade: | K9F1G08U0A-PIB0 (1Gb) or equipollent * 1 |

|               | Standard Grade:   | K9F2G08U0A-PCB0 (2Gb) or equipollent * 1 |

|               |                   | K9F1G08U0A-PCB0(1Gb) or equipollent * 2  |

| 256MB         | Industrial Grade: | K9F2G08U0A-PIB0 (2Gb) or equipollent * 1 |

|               |                   | K9F1G08U0A-PIB0 (1Gb) or equipollent * 2 |

|               | Standard Grade:   | K9F4G08U0M-PCB0 (4Gb) or equipollent * 1 |

|               |                   | K9F2G08U0A-PCB0 (2Gb) or equipollent * 2 |

| 5/015         |                   | K9F1G08U0A-PCB0(1Gb) or equipollent * 4  |

| 512MB         | Industrial Grade: | K9F4G08U0M-PIB0 (4Gb) or equipollent * 1 |

|               |                   | K9F2G08U0A-PIB0 (2Gb) or equipollent * 2 |

|               |                   | K9F1G08U0A-PIB0 (1Gb) or equipollent * 4 |

|               | Standard Grade:   | K9K8G08U0M-PCB0 (8Gb) or equipollent * 1 |

| 1GB           |                   | K9F4G08U0M-PCB0 (4Gb) or equipollent * 2 |

| IGB           | Industrial Grade: | K9K8G08U0M-PIB0 (8Gb) or equipollent * 1 |

|               |                   | K9F4G08U0M-PIB0 (4Gb) or equipollent * 2 |

|               | Standard Grade:   | K9WAG08U1M-PCB0 (16Gb) or equipollent *1 |

| 2GB           |                   | K9K8G08U0M-PCB0 (8Gb) or equipollent *2  |

| 266           | Industrial Grade: | K9WAG08U1M-PIB0 (16Gb) or equipollent *1 |

|               |                   | K9K8G08U0M-PIB0 (8Gb) or equipollent *2  |

|               | Standard Grade:   | K9WAG08U1M-PCB0 (16Gb) or equipollent *2 |

| 4GB           |                   | K9K8G08U0M-PCB0 (8Gb) or equipollent *4  |

| 408           | Industrial Grade: | K9WAG08U1M-PIB0 (16Gb) or equipollent *2 |

|               |                   | K9K8G08U0M-PIB0 (8Gb) or equipollent *4  |

| 8GB           | Standard Grade:   | K9WAG08U1M-PCB0 (16Gb) or equipollent *4 |

| 008           | Industrial Grade: | K9WAG08U1M-PIB0 (16Gb) or equipollent *4 |

Table 6: Card Configuration vs. Samsung NAND SLC part number

The table 7 shows the specific capacity for the various models and the default number of heads, sectors/track and cylinders.

| Unformatted Capacity | Default Cylinder | Default Head | Default Sector | Default CHS<br>Capacity |

|----------------------|------------------|--------------|----------------|-------------------------|

| 128MB                | 500              | 16           | 32             | 256,000                 |

| 256MB                | 1,000            | 16           | 32             | 512,000                 |

| 512MB                | 1,015            | 16           | 63             | 1,023,120               |

| 1,024MB              | 2,031            | 16           | 63             | 2,047,248               |

| 2.04GB               | 4,063            | 16           | 63             | 4,095,504               |

| 4GB                  | 8,146            | 16           | 63             | 8,211,168               |

| 8GB                  | 16,000           | 16           | 63             | 16,128,000              |

#### Table 7: Model Capacity

# 3. Interface Description

# 3.1. Physical Description

The pin 1 ~ pin 44 are for IDE interface.

#### 3.2. Pin Assignments

Signals whose source is the host is designated as inputs while signals that the Industrial 44-pin micro IDE Flash (MIF) Disk sources are outputs. The pin assignments are listed in below table 8.

| Table 8: Pin Assignments         |                                                 |                                                                                                                  |                                  |                                                |                                                                                                       |              |

|----------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------|

| Pin No.                          | Signal Name                                     | Description                                                                                                      | Pin No.                          | Pin Name                                       | Description                                                                                           |              |

| 1                                | HRESET                                          | Host Reset                                                                                                       | 2                                | GND                                            | Ground                                                                                                |              |

| 3                                | HDB[7]                                          | Host Data Bit 7                                                                                                  | 4                                | HDB[8]                                         | Host Data Bit 8                                                                                       |              |

| 5                                | HDB[6]                                          | Host Data Bit 6                                                                                                  | 6                                | HDB[9]                                         | Host Data Bit 9                                                                                       |              |

| 7                                | HDB[5]                                          | Host Data Bit 5                                                                                                  | 8                                | HDB[10]                                        | Host Data Bit 10                                                                                      |              |

| 9                                | HDB[4]                                          | Host Data Bit 4                                                                                                  | 10                               | HDB[11]                                        | Host Data Bit 11                                                                                      |              |

| 11                               | HDB[3]                                          | Host Data Bit 3                                                                                                  | 12                               | HDB[12]                                        | Host Data Bit 12                                                                                      |              |

| 13                               | HDB[2]                                          | Host Data Bit 2                                                                                                  | 14                               | HDB[13]                                        | Host Data Bit 13                                                                                      |              |

| 15                               | HDB[1]                                          | Host Data Bit 1                                                                                                  | 16                               | HDB[14]                                        | Host Data Bit 14                                                                                      |              |

| 17                               | HDB[0]                                          | Host Data Bit 0                                                                                                  | 18                               | HDB[15]                                        | Host Data Bit 15                                                                                      |              |

| 19                               | GND                                             | Ground                                                                                                           | 20                               | KEY <sup>1</sup>                               | Key-pin                                                                                               |              |

| 21                               | DMARQ                                           | DMA Request                                                                                                      | 22                               | GND                                            | Ground                                                                                                |              |

|                                  | HIOW <sup>3</sup>                               | Host I/O Write                                                                                                   |                                  | 0.4                                            | GND                                                                                                   |              |

| 23                               | STOP⁴                                           | Stop Ultra DMA burst                                                                                             | 24                               | 24                                             |                                                                                                       |              |

|                                  | HIOR <sup>3</sup>                               | Host I/O Read                                                                                                    |                                  | GND                                            | Ground                                                                                                |              |

| 25                               | HDMARDY <sup>4</sup>                            | Ultra DMA ready                                                                                                  | 26                               |                                                |                                                                                                       |              |

|                                  | HSTROBE <sup>4</sup>                            | Ultra DMA data strobe                                                                                            |                                  |                                                |                                                                                                       |              |

|                                  | IORDY <sup>3</sup>                              | I/O Ready                                                                                                        |                                  |                                                |                                                                                                       |              |

| 27                               | DDMARDY <sup>4</sup>                            | Ultra DMA ready                                                                                                  | 28                               | 28                                             | CSEL                                                                                                  | Cable select |

|                                  | DSTROBE <sup>4</sup>                            | Ultra DMA data strobe                                                                                            |                                  |                                                |                                                                                                       |              |

| 29                               | DMACK                                           | DMA Acknowledge                                                                                                  | 30                               | GND                                            | Ground                                                                                                |              |

| 31                               | INTRQ                                           | Interrupt Request                                                                                                | 32                               | IOCS16                                         | CS I/O 16-Bit                                                                                         |              |

| 33                               | HAB[1]                                          | Host Address Bit 1                                                                                               | 34                               | PDIAG                                          | Passed Diagnostic                                                                                     |              |

| 35                               | HAB[0]                                          | Host Address Bit 0                                                                                               | 36 HAB[2] Host Addre             |                                                | Host Address Bit 2                                                                                    |              |

| 37                               | CS0                                             | Chip Select 0                                                                                                    | 38 CS1                           |                                                | Chip Select 1                                                                                         |              |

| 39                               | DASP                                            | Drive Active                                                                                                     | 40                               | GND                                            | Ground                                                                                                |              |

| 41                               | VCC                                             | Supply Voltage                                                                                                   | 42                               | VCC                                            | Supply Voltage                                                                                        |              |

| 43 GND Ground                    |                                                 | 44 <sup>2</sup>                                                                                                  | NC                               | Not Connected                                  |                                                                                                       |              |

| 31<br>33<br>35<br>37<br>39<br>41 | INTRQ<br>HAB[1]<br>HAB[0]<br>CS0<br>DASP<br>VCC | Interrupt Request<br>Host Address Bit 1<br>Host Address Bit 0<br>Chip Select 0<br>Drive Active<br>Supply Voltage | 32<br>34<br>36<br>38<br>40<br>42 | IOCS16<br>PDIAG<br>HAB[2]<br>CS1<br>GND<br>VCC | CS I/O 16-Bit<br>Passed Diagnostic<br>Host Address Bit 2<br>Chip Select 1<br>Ground<br>Supply Voltage |              |

Table 8: Pin Assignments

In the 44-pin version, this pin is defined as KEY, according to the ATA standard.

NC = These pins are not connected internally.

Signal usage in PIO & Multiword DMA mode.

Signal usage in Ultra DMA mode.

### 3.3. Electrical Description

The Industrial 40/44-pin micro IDE Flash (MIF) Disk Hermit Series is optimized for operation with hosts. .Table 9: describes the signals of 40/44-pin interface.

| 39DASP-I/Ois present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCCVCCConnect to VCC2, 19, 22, 24,GNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin No.                                             | Signal Name          | Туре                | Description                                                            |                     |     |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------|---------------------|------------------------------------------------------------------------|---------------------|-----|-----------------|

| 38  CS1-  I  Chip select CS1    31  INTRQ  O  Host interrupt signal.    25  HDMARDY- <sup>4</sup> I  DMA ready during Ultra DMA data in burst    23  HIOK- <sup>3</sup> I  DMA ready during Ultra DMA data out burst    23  HIOK- <sup>3</sup> I  I/O read strobe signal.    23  STOP <sup>4</sup> I  I/O read strobe signal.    32  IOCS16-  O  Asserted in 16-bit access.    10RDY <sup>3</sup> I/O Ready Signal  DMA ready during Ultra DMA data out burst    27  DDMARDY- <sup>4</sup> O  DA ready during Ultra DMA data out burst    10, 8, 6, 4, 3, 5, 7, 9, 11, 13, 15, 17  I/O  Host data bus    33, 35, 36  HAB[2:0]  I/O  Host Address bus    33, 35, 36  HAB[2:0]  I/O  Host Address bus    39  DASP-  I/O  Host as an input port to check in the slave mode to see if the slave is present or not.    34  PDIAG-  I/O  O  DMA Request.    29  DMACK-  I  DMA Request.  I/O MA Request.    29  DMACK-  I  DMA Ready during Ultra DMA data out port to return the result of diagnosis in the master.    21  DMARQ  O  DMA Ready during Ultra DMA data out burst    29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                   | HRESET-              | I                   | Host reset signal, High: Reset.                                        |                     |     |                 |

| 31  INTRQ  O  Host interrupt signal.    25  HIOR. <sup>3</sup> I  I/O read strobe signal.    23  HIOW. <sup>3</sup> I  DMA ready during Ultra DMA data in burst    23  HIOW. <sup>3</sup> I  I/O wite strobe signal.    32  IOCS16-  O  Asserted in 16-bit access.    32  IOCS16-  O  Asserted in 16-bit access.    10  DMARDY. <sup>4</sup> O  DMA ready during Ultra DMA data out burst    11  Stop during Ultra DMA data out burst  I/O write strobe signal.    32  IOCS16-  O  Asserted in 16-bit access.    10  DMARDY. <sup>4</sup> O  DMA ready during Ultra DMA data out burst    18, 16, 14, 12, 10, 8, 6, 4, 3, 5, 7, 9, 11, 13, 15, 17  HOB[15:0]  I/O    33, 35, 36  HAB[2:0]  I/O  Host data bus    28  CSEL-1  I  Low: Device operates as a master, High: Device operates as a slave. Switch used.    39  DASP-  I/O  Used as an input port to check in the master mode to see if the slave for the master is present or not.    34  PDIAG-  I/O  Used as an input port to check in the slave diagnosis in the master.    39  DMARQ  O  DMA Request.    29  DMACK-  I  DMA Acknowledge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                  | CS0-                 | I                   | Chip select CS0                                                        |                     |     |                 |

| $\begin{array}{ c c c c } & HOR^3 & HOR^3 & HOR^3 & HOR^3 & HOR^3 & HORARDY^4 & I & DMA ready during Ultra DMA data in burst \\ \hline HSTROBE^4 & I & DMA ready during Ultra DMA data out burst & Data strobe signal. \\ \hline HOW.^3 & I & STOP^4 & I & Stop during Ultra DMA data out burst & IO write strobe signal. \\ \hline STOP^4 & O & Asserted in 16-bit access. & IORDY^3 & DDMARDY^4 & O & DMA ready during Ultra DMA data out burst & DATA data bus & STOP & DATA data out burst & DATA data bus & STOP & DATA data out burst & DATA data bus & STOP & DATA data out burst & DATA data bus & STOP & IONA data out burst & DATA data bus & STOP & IONA data out burst & DATA data bus & STOP & IONA data bus & STOP & ST$ | 38                                                  | CS1-                 | I                   | Chip select CS1                                                        |                     |     |                 |

| 25      HDMARDY. <sup>4</sup> I      DMA ready during Ultra DMA data in burst        23      HIOW. <sup>3</sup> I      Data strobe during Ultra DMA data out burst        23      HIOW. <sup>3</sup> I      Vorite strobe signal.        32      IOCS16-      O      Asserted in 16-bit access.        32      IOCS16-      O      Asserted in 16-bit access.        707      DDMARDY. <sup>4</sup> O      Asserted in 16-bit access.        10RDY <sup>3</sup> IORDY <sup>3</sup> IOR Ready Signal      IOR        70      DDMARDY. <sup>4</sup> O      Asserted in 16-bit access.      IOR        10, 8, 6, 4, 3, 5, 7, 9, 11, 13, 15, 17      IOE[15:0]      I/O      Data strobe during Ultra DMA data out burst      IDA        33, 35, 36      HAB[2:0]      I/O      Host Address bus      IOR        38      CSEL-1      I      Low: Device operates as a master, High: Device operates as a slave. Switch used.        39      DASP-      I/O      Host Address bus      Ise as an input port to check in the master mode to see if the slave mode to see if the slave for the master is present or not.        34      PDIAG-      I/O      Used as an input port to check in the result of slave diagnosis in the master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                  | INTRQ                | 0                   | Host interrupt signal.                                                 |                     |     |                 |

| HSTROBE <sup>4</sup> Data strobe during Ultra DMA data out burst        23      HIOW- <sup>3</sup> I      I/O write strobe signal.        32      IOCS16-      O      Asserted in 16-bit access.        32      IOCS16-      O      Asserted in 16-bit access.        10RDY <sup>3</sup> I/O Ready Signal      I/O Ready Signal        27      DDMARDY. <sup>4</sup> O      DMA ready during Ultra DMA data out burst        18, 16, 14, 12,      DSTROBE <sup>4</sup> O      Host data bus        18, 16, 14, 12,      HDB[15:0]      I/O      Host data bus        15, 17      HDB[15:0]      I/O      Host Address bus        33, 35, 36      HAB[2:0]      I/O      Host Address bus        28      CSEL-1      I      Low: Device operates as a master, High: Device operates as a slave. Switch used.        39      DASP-      I/O      Used as an input port to check in the slave mode to see if the slave for the master is present or not.        34      PDIAG-      I/O      DMA Request.        29      DMACK-      I      DMA Acknowledge.        20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC      VCC      Connect to VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     | HIOR- <sup>3</sup>   |                     | I/O read strobe signal.                                                |                     |     |                 |

| 23    HIOW. <sup>3</sup> I    I/O write stroke signal.      32    IOCS16-    O    Asserted in 16-bit access.      27    IORDY <sup>3</sup> I/O Ready Signal    I/O Ready Signal      27    DDMARDY. <sup>4</sup> O    DMA ready during Ultra DMA data out burst      18, 16, 14, 12,    IOS TROBE <sup>4</sup> O    Host data bus      15, 7, 9, 11, 13,    HDB[15:0]    I/O    Host data bus      33, 35, 36    HAB[2:0]    I/O    Host Address bus      28    CSEL-1    I    Low: Device operates as a master, High: Device operates as a slave. Switch used.      39    DASP-    I/O    Used as an input port to check in the master mode to see if the slave for the master is present or not.      34    PDIAG-    I/O    Used as an input port to evaluate the result of slay ediagnosis in the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA cknowledge.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                  | HDMARDY-4            | 1                   | DMA ready during Ultra DMA data in burst                               |                     |     |                 |

| 23STOP4IStop during Ultra DMA data bursts32IOCS16-OAsserted in 16-bit access.27DDMARDY-4ODMA ready Signal27DDMARDY-4ODMA ready during Ultra DMA data out burst18, 16, 14, 12,<br>10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17DB[15:0]I/O33, 35, 36HAB[2:0]I/OHost data bus28CSEL-1ILow: Device operates as a master, High: Device operates as a slave.<br>Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA cknowledge.20', 41', 42'VCCVCCConnect to VCC2, 19, 22, 24,<br>2, 19, 22, 24,GNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     | HSTROBE <sup>4</sup> |                     | Data strobe during Ultra DMA data out burst                            |                     |     |                 |

| STOP*Stop during Ultra DMA data bursts32IOCS16-OAsserted in 16-bit access.10RDY3DMARDY.4OI/O Ready Signal27DDMARDY.4ODMA ready during Ultra DMA data out burst18, 16, 14, 12,<br>10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17DB[15:0]I/OHost data bus33, 35, 36HAB[2:0]I/OHost Address bus28CSEL-1ILow: Device operates as a master, High: Device operates as a slave.<br>Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Request.20, 14, 12, 22, 24,<br>2, 19, 22, 24,GNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     | HIOW- <sup>3</sup>   |                     | I/O write strobe signal.                                               |                     |     |                 |

| IORDV <sup>3</sup> DDMARDY-4    O    I/O Ready Signal      27    DDMARDY-4    O    DMA ready during Ultra DMA data out burst      18, 16, 14, 12,    INORDE4    Data strobe during Ultra DMA data in burst      10, 8, 6, 4, 3,    For Strope 1    INORDE4    Data strobe during Ultra DMA data in burst      18, 16, 14, 12,    INORDE4    INORDE4    Data strobe during Ultra DMA data in burst      10, 8, 6, 4, 3,    For Strope 1    INORDE4    Host data bus      5, 7, 9, 11, 13,    IS    INORDE4    Host datas bus      33, 35, 36    HAB[2:0]    INO    Host Address bus      28    CSEL-1    I    Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.      39    DASP-    INO    Used as an input port to check in the master mode to see if the slave is present or not.      34    PDIAG-    INO    Used as an input port to evaluate the result of slave diagnosis in the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA Acknowledge.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC      2, 19, 22, 24,    GND    GND    Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23                                                  | STOP <sup>4</sup>    | I                   | Stop during Ultra DMA data bursts                                      |                     |     |                 |

| 27    DDMARDY-4    O    DMA ready during Ultra DMA data out burst      18, 16, 14, 12,    DSTROBE4    Data strobe during Ultra DMA data in burst      10, 8, 6, 4, 3,    HDB[15:0]    I/O    Host data bus      33, 35, 36    HAB[2:0]    I/O    Host Address bus      28    CSEL-1    I    Master/Slave select signal (cable select signal).      28    CSEL-1    I    Low: Device operates as a master, High: Device operates as a slave.      39    DASP-    I/O    Used as an input port to check in the master mode to see if the slave is present or not.      34    PDIAG-    I/O    Used as an input port to evaluate the result of slave diagnosis in the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA Request.      29    DMACK-    I    DMA Request.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC      2, 19, 22, 24,    GND    GND    Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                                  | IOCS16-              | 0                   | Asserted in 16-bit access.                                             |                     |     |                 |

| DSTROBE*  Data strobe during Ultra DMA data in burst    18, 16, 14, 12,<br>10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17  HDB[15:0]  I/O  Host data bus    33, 35, 36  HAB[2:0]  I/O  Host Address bus    33, 35, 36  HAB[2:0]  I/O  Host Address bus    28  CSEL-1  I  Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.    39  DASP-  I/O  Used as an input port to check in the master mode to see if the slave is present or not, and as an output port to check in the slave mode to see if the slave mode to see if the slave for the master is present or not.    34  PDIAG-  I/O  Used as an input port to evaluate the result of slave diagnosis in the master.    21  DMARQ  O  DMA Request.    29  DMACK-  I  DMA Acknowledge.    20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC  VCC  Connect to VCC    2, 19, 22, 24,  GND  GND  Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     | IORDY <sup>3</sup>   |                     | I/O Ready Signal                                                       |                     |     |                 |

| 18, 16, 14, 12,<br>10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17    HDB[15:0]    I/O    Host data bus      33, 35, 36    HAB[2:0]    I/O    Host Address bus      33, 35, 36    HAB[2:0]    I/O    Host Address bus      28    CSEL-1    I    Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.      39    DASP-    I/O    Used as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.      34    PDIAG-    I/O    Used as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA Acknowledge.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC      2, 19, 22, 24,    GND    GND    Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                  | DDMARDY-4            | 0                   | DMA ready during Ultra DMA data out burst                              |                     |     |                 |

| 10, 8, 6, 4, 3,<br>5, 7, 9, 11, 13,<br>15, 17HDB[15:0]I/OHost data bus33, 35, 36HAB[2:0]I/OHost Address bus33, 35, 36HAB[2:0]I/OHost Address bus28CSEL-1IMaster/Slave select signal (cable select signal).<br>Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.201, 41², 42²VCCVCCConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     | DSTROBE <sup>4</sup> |                     | Data strobe during Ultra DMA data in burst                             |                     |     |                 |

| 5, 7, 9, 11, 13,<br>15, 17HDB[15:0]I/OHost data bus33, 35, 36HAB[2:0]I/OHost Address bus33, 35, 36HAB[2:0]I/OHost Address bus28CSEL-1ILow: Device operates as a master, High: Device operates as a slave.<br>Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.201, 41², 42²VCCVCCConnect to VCC2, 19, 22, 24,<br>GNDGNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18, 16, 14, 12,                                     |                      |                     |                                                                        |                     |     |                 |

| 5, 7, 9, 11, 13,    Image: Constraint of the standard state of the                                                                          | 10, 8, 6, 4, 3,                                     | HDB[15:0]            | I/O                 | Host data bus                                                          |                     |     |                 |

| 33, 35, 36    HAB[2:0]    I/O    Host Address bus      33, 35, 36    HAB[2:0]    I/O    Host Address bus      28    CSEL-1    I    Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.      39    DASP-    I/O    Used as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.      34    PDIAG-    I/O    Used as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA Acknowledge.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC      2, 19, 22, 24,    GND    GND    Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5, 7, 9, 11, 13,                                    |                      |                     |                                                                        |                     |     |                 |

| 28    CSEL-1    I    Master/Slave select signal (cable select signal).<br>Low: Device operates as a master, High: Device operates as a slave.<br>Switch used.      39    DASP-    I/O    Used as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.      34    PDIAG-    I/O    Used as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.      21    DMARQ    O    DMA Request.      29    DMACK-    I    DMA Acknowledge.      20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCC    VCC    Connect to VCC      2, 19, 22, 24,    GND    GND    Connect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15, 17                                              |                      |                     |                                                                        |                     |     |                 |

| 28CSEL-1ILow: Device operates as a master, High: Device operates as a slave.<br>Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCCVCCConnect to VCC2, 19, 22, 24,<br>CGNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33, 35, 36                                          | HAB[2:0]             | I/O                 | Host Address bus                                                       |                     |     |                 |

| Switch used.39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCCVCCConnect to VCC2, 19, 22, 24,GNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     | 28 CSEL- I           | I                   | Master/Slave select signal (cable select signal).                      |                     |     |                 |

| 39DASP-I/OUsed as an input port to check in the master mode to see if the slave<br>is present or not, and as an output port to check in the slave mode to<br>see if the slave for the master is present or not.34PDIAG-I/OUsed as an input port to evaluate the result of slave diagnosis in the<br>master mode, and as an output port to return the result of diagnosis<br>to the master.21DMARQODMA Request.29DMACK-IDMA Acknowledge.20 <sup>1</sup> , 41 <sup>2</sup> , 42 <sup>2</sup> VCCVCCConnect to VCC2, 19, 22, 24,GNDGNDConnect to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                                                  |                      |                     | Low: Device operates as a master, High: Device operates as a slave.    |                     |     |                 |